About Me

Welcome to my portfolio! I am Marwan Abdelwahab, a Computer Engineering student at the University of South Florida passionate about building intelligent, reliable, and efficient computing systems that bridge hardware design, embedded software, and artificial intelligence.

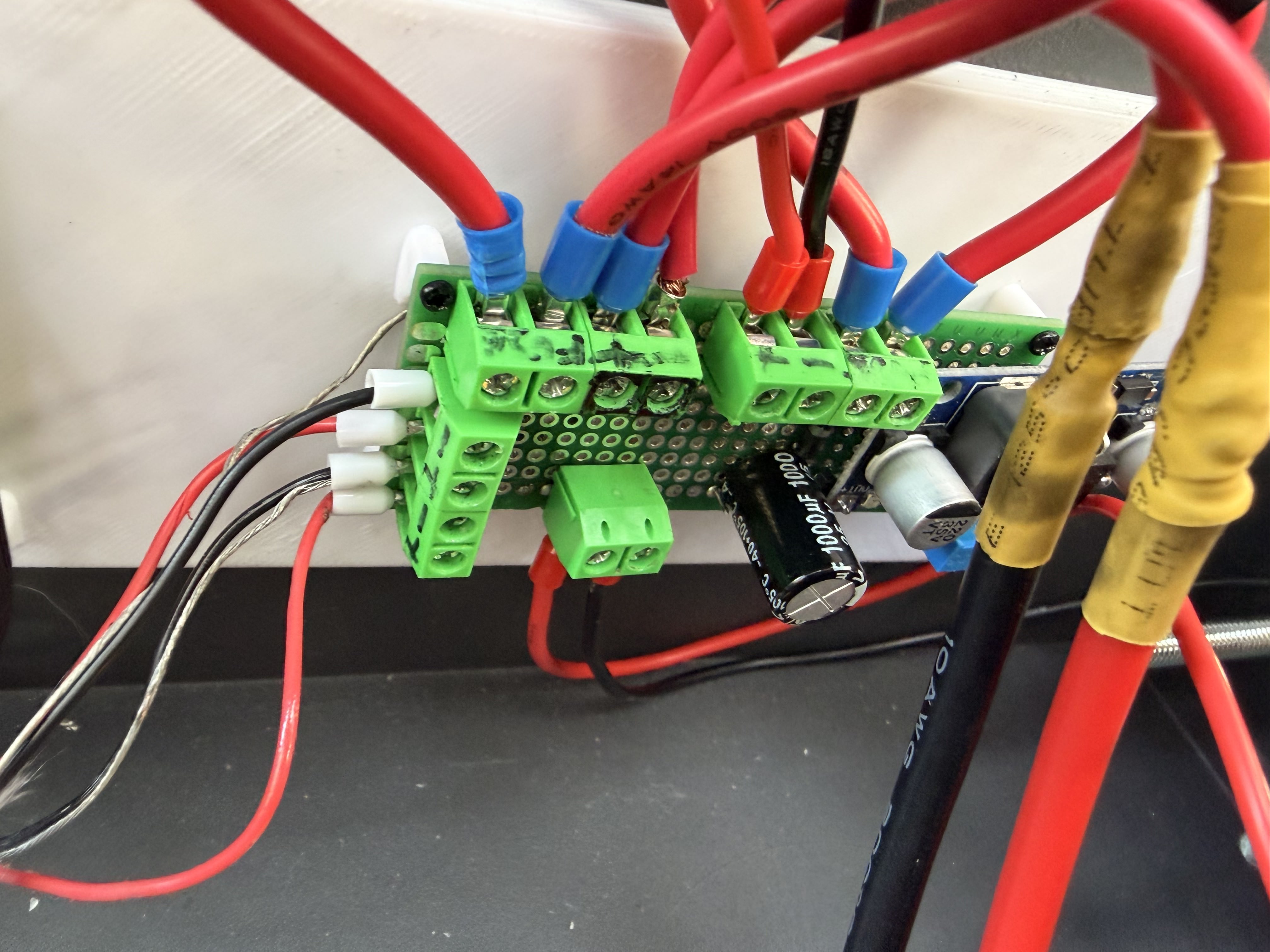

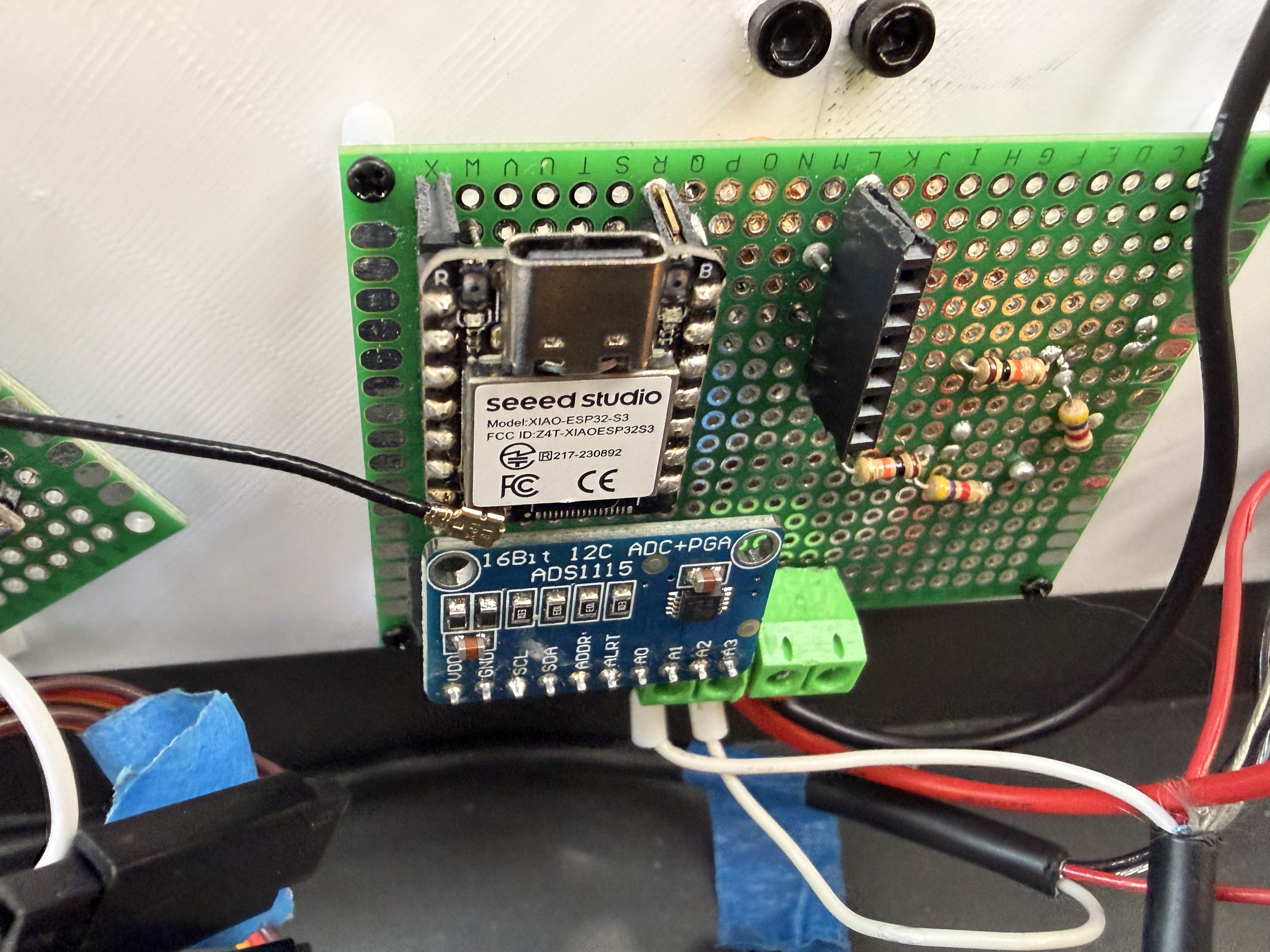

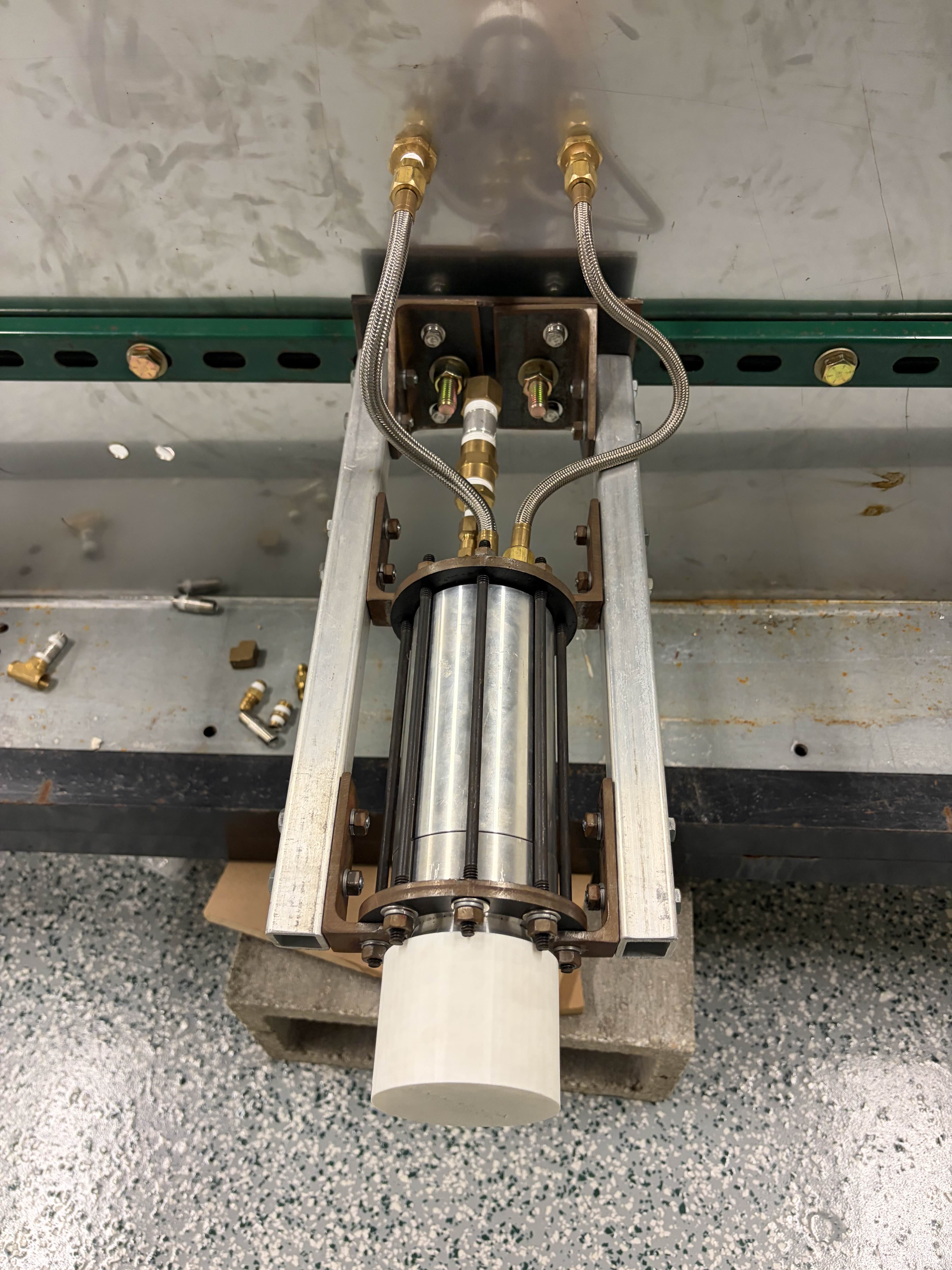

I currently serve as the Electronics Team Lead for the Society of Aeronautics and Rocketry (SOAR), where I lead the design and integration of real-time data acquisition and control systems for a student-built liquid rocket engine. My work spans FreeRTOS firmware development in C++, sensor interfacing, and custom PCB design, enabling reliable telemetry and control under demanding test conditions.

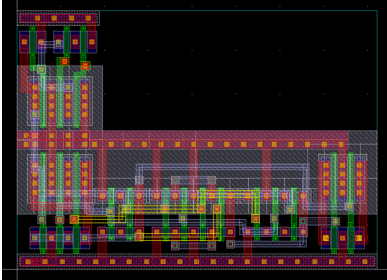

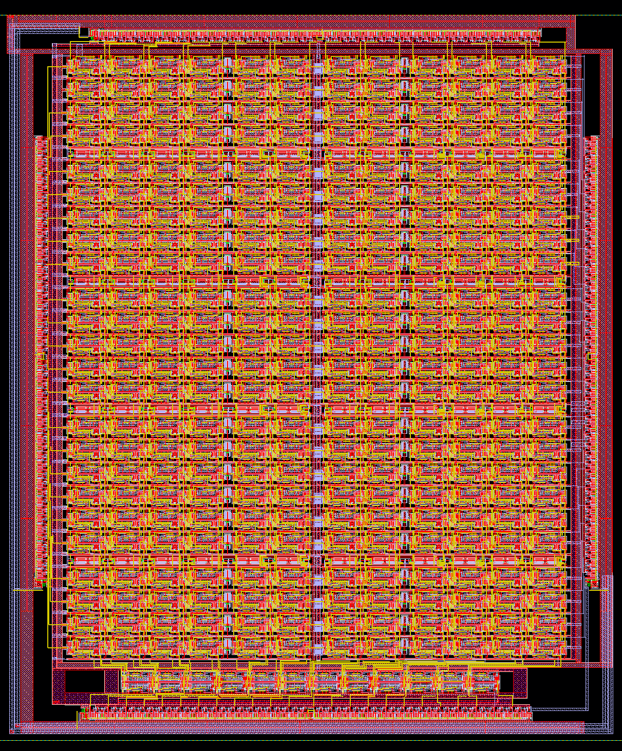

At the SEES Lab, I conduct research on Generative AI for hardware design, developing large language model-based methods for automating RTL code generation and verification. My current focus is on building a hierarchical Verilog dataset for benchmarking AI-assisted circuit design and evaluating performance, power, and area trade-offs using Yosys, OpenLane, and the Sky130 PDK.

Previously, I designed a RISC-V SoC with a machine learning accelerator, integrating a custom coprocessor and producing a DRC/LVS-clean GDSII layout as part of my ASIC design research.

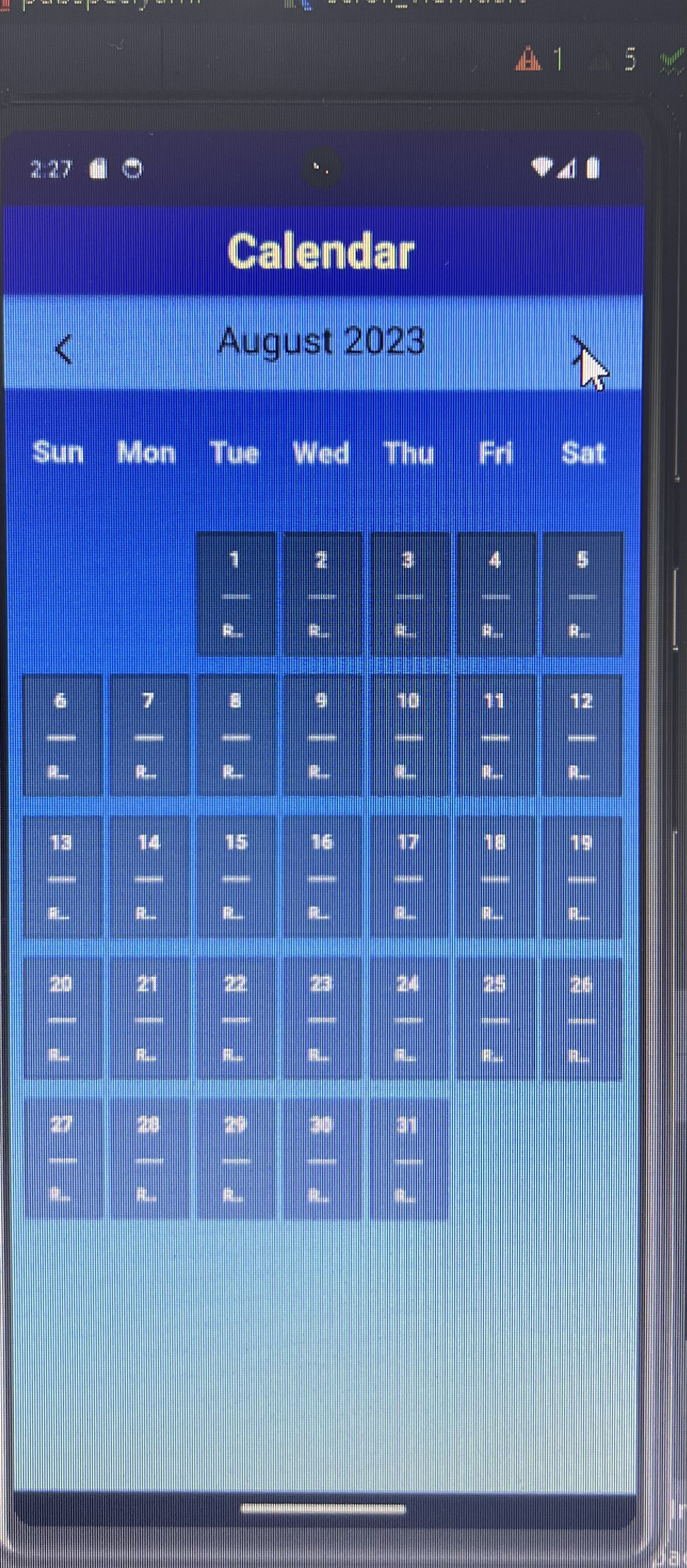

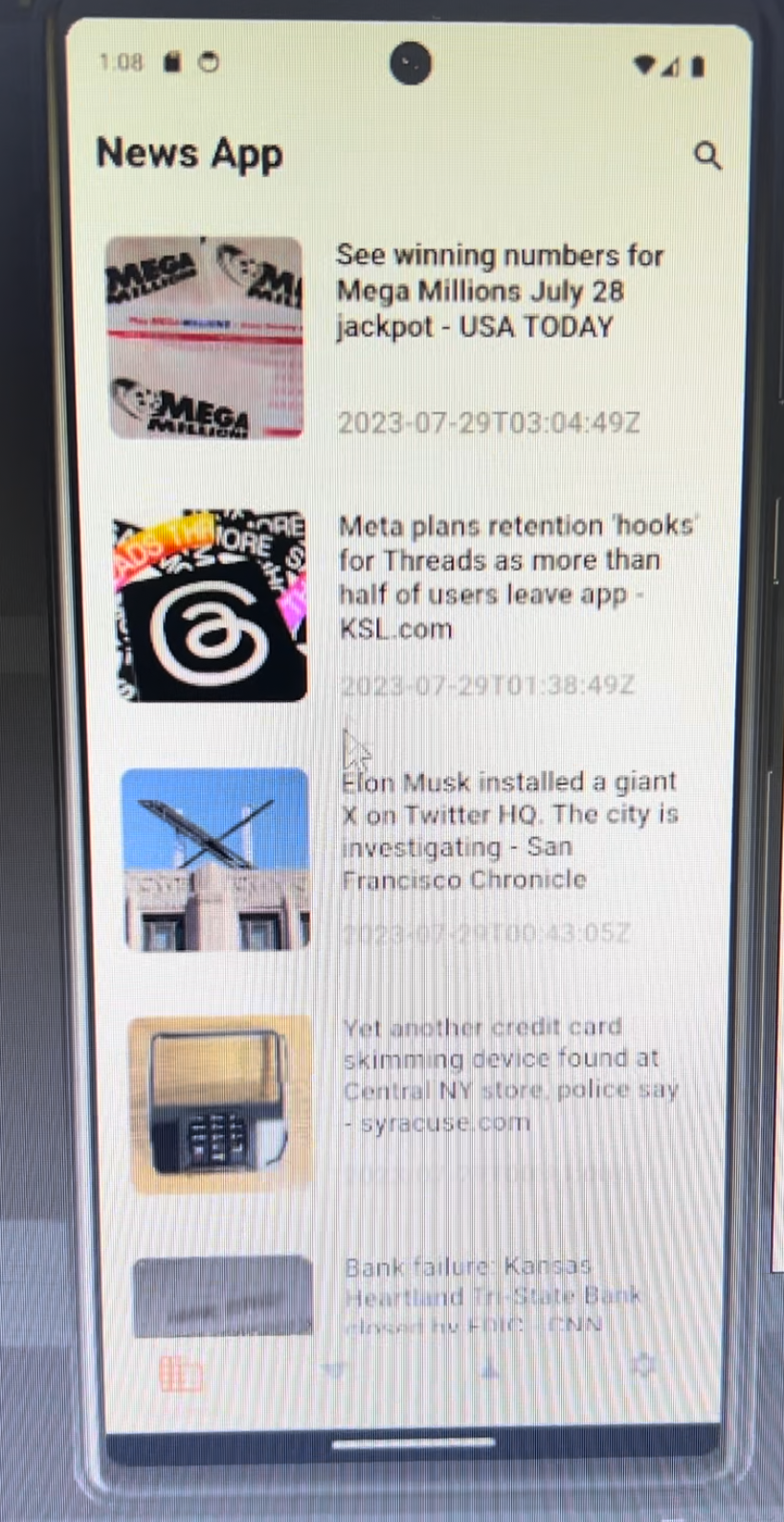

Alongside research, I work as a Teaching Assistant for Computer Logic & Design, mentoring over 100 students in Verilog, digital design, and simulation workflows. I also serve as an Operations Assistant for USF Housing & Residential Education, where I strengthen my organizational and communication skills by managing equipment logistics and student support tasks.

Driven by curiosity and precision, I aim to advance in the intersection of embedded systems, AI-driven hardware design, and digital system optimization—building the technologies that connect intelligent software with efficient hardware.

Here is a link to my resume. Check it out!